# Technical Support Center: Optimizing Annealing Processes for Ion-Implanted Silicon-28

**Author:** BenchChem Technical Support Team. **Date:** December 2025

## Compound of Interest

Compound Name: *Silicon28*

Cat. No.: *B1172460*

[Get Quote](#)

This technical support center provides troubleshooting guidance and frequently asked questions (FAQs) for researchers, scientists, and drug development professionals working with ion-implanted Silicon-28. The information is designed to address specific issues encountered during experimental procedures.

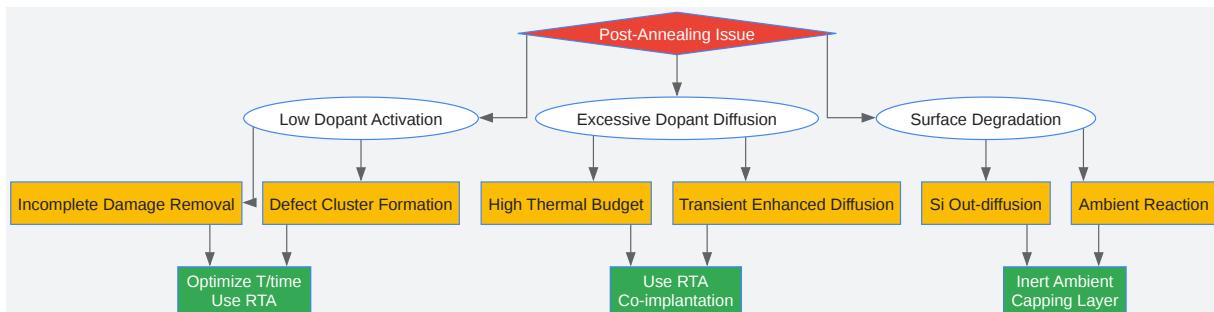

## Troubleshooting Guide

This guide addresses common problems encountered during the annealing of ion-implanted Silicon-28, offering potential causes and solutions in a question-and-answer format.

**Question 1:** After annealing, electrical measurements indicate low dopant activation. What are the possible causes and how can I improve it?

**Answer:** Low electrical activation of implanted impurities is a frequent issue. The primary goal of annealing is to repair crystal damage and move implanted ions into substitutional lattice sites, making them electrically active.[1][2]

- **Incomplete Damage Removal:** The annealing temperature or time may be insufficient to repair the lattice damage caused by ion implantation.[1][2] Crystal defects like vacancies, interstitials, and amorphous zones can trap dopants in electrically inactive sites.[1]

- **Formation of Defect Clusters:** At certain temperature ranges (e.g., 500-600°C), dislocations can form, which may capture impurity atoms, reducing their electrical activity.[1]

- Inappropriate Annealing Ambient: The annealing environment can influence dopant activation. For certain materials, annealing in a nitrogen (N<sub>2</sub>) or argon (Ar) atmosphere is recommended to prevent unwanted reactions.[1][3]

Solutions:

- Optimize Annealing Temperature and Time: Increase the annealing temperature or duration. Temperatures between 900°C and 1100°C are often optimal for activating dopants in silicon. [4] However, the exact parameters depend on the dopant and implant dose.

- Rapid Thermal Annealing (RTA): Consider using RTA to achieve high temperatures quickly, which can help to dissolve dislocations and activate dopants while minimizing dopant diffusion.[3]

- Control the Annealing Ambient: Ensure the annealing is performed in a neutral environment like N<sub>2</sub> or Ar to prevent oxidation or other unintended surface reactions.[1]

Question 2: Significant dopant diffusion is observed after annealing, leading to broadened profiles and junction degradation. How can this be mitigated?

Answer: Dopant diffusion during annealing is a significant concern, especially for creating shallow junctions in modern electronic devices.[1]

- Excessive Thermal Budget: High annealing temperatures and long annealing times, while promoting dopant activation, also enhance diffusion.

- Transient Enhanced Diffusion (TED): Implantation damage can lead to an excess of silicon interstitials, which can significantly enhance the diffusion of dopants like boron and phosphorus during subsequent annealing.

Solutions:

- Rapid Thermal Annealing (RTA): RTA is a key technique to minimize diffusion. It provides a high thermal budget for a very short duration, activating the dopants with minimal movement.

- Lower Temperature Annealing: For some applications, a lower annealing temperature for a longer duration might be a viable trade-off to limit diffusion, although this could impact dopant

activation.

- Co-implantation: Co-implanting species like carbon can help to reduce transient enhanced diffusion by acting as traps for interstitials.

Question 3: The surface morphology of the silicon wafer is degraded after annealing, showing roughness or pitting. What causes this and how can it be prevented?

Answer: Surface degradation during high-temperature annealing can be a significant issue, particularly for materials like Silicon Carbide (SiC) where it's referred to as step-bunching, but similar principles apply to Silicon-28.[\[2\]](#)[\[5\]](#)

- Silicon Out-diffusion: At very high temperatures, silicon atoms can sublimate from the surface, leading to a roughened morphology.[\[2\]](#)

- Reaction with Ambient Gases: The annealing ambient, if not inert, can react with the silicon surface. For example, residual oxygen can lead to the formation of a non-uniform oxide layer.

Solutions:

- Silane Overpressure: For SiC, and potentially adaptable for Si-28 under specific conditions, introducing a silane (SiH4) overpressure during annealing can suppress the out-diffusion of silicon from the lattice.[\[2\]](#)[\[5\]](#)

- High Purity Inert Ambient: Use a high-purity inert gas flow (e.g., Ar or N2) to minimize reactions with the silicon surface.[\[1\]](#)

- Capping Layer: In some processes, a capping layer (e.g., silicon nitride) is deposited before annealing to protect the surface and is subsequently removed.

## Frequently Asked Questions (FAQs)

Q1: What is the primary purpose of annealing after ion implantation in Silicon-28?

A1: The primary purposes of annealing are twofold: to repair the crystal lattice damage caused by the energetic ions and to electrically activate the implanted dopant atoms by encouraging them to move into substitutional sites within the silicon lattice.[\[1\]](#)[\[2\]](#)

Q2: What are the common types of defects generated during ion implantation?

A2: Ion implantation can create a variety of crystal defects, including:

- Point defects: Vacancies (missing atoms) and interstitials (atoms in non-lattice sites).[\[1\]](#)

- Defect clusters: Di-vacancies and higher-order vacancy clusters.[\[1\]](#)

- Amorphous zones: Localized regions where the crystalline structure is destroyed.[\[1\]](#)

- Dislocations and stacking faults: Extended defects that can form during the annealing process itself.[\[3\]\[6\]](#)

Q3: What is the difference between furnace annealing and rapid thermal annealing (RTA)?

A3:

- Furnace Annealing: Involves heating the wafer in a furnace for a relatively long duration (minutes to hours) at a specific temperature.

- Rapid Thermal Annealing (RTA): Uses high-intensity lamps to rapidly heat the wafer to a high temperature for a short period (seconds). RTA is often preferred to activate dopants while minimizing their diffusion.[\[3\]](#)

Q4: How does the annealing ambient affect the process?

A4: The annealing ambient is critical. Annealing is typically conducted in a neutral environment, such as argon (Ar) or nitrogen (N<sub>2</sub>), to prevent the silicon surface from reacting with oxygen or other contaminants.[\[1\]](#) An oxygen-containing ambient can lead to the formation of oxidation-induced stacking faults.[\[3\]](#)

Q5: What are typical annealing temperatures for dopants in silicon?

A5: The optimal annealing temperature depends on the implanted dopant and the desired outcome. Generally, temperatures in the range of 900°C to 1100°C are used for dopant activation in silicon.[\[4\]](#) However, lower temperatures (500-600°C) can be used for solid-phase epitaxial regrowth of amorphous layers.[\[1\]](#)

## Quantitative Data Summary

The following tables summarize key quantitative data from various experimental studies on annealing ion-implanted silicon and related materials.

Table 1: Annealing Parameters for Different Implanted Ions in Silicon

| Implanted Ion | Energy (keV) | Fluence (cm <sup>-2</sup> ) | Annealing Temperature (°C) | Annealing Time           | Key Observation                                                                             |

|---------------|--------------|-----------------------------|----------------------------|--------------------------|---------------------------------------------------------------------------------------------|

| Phosphorus    | 5            | 1 x 10 <sup>15</sup>        | 600 - 1000                 | 30 s                     | Outdiffusion observed at lower temperatures; indiffusion at 1000°C. [7]                     |

| Phosphorus    | 10           | 5 x 10 <sup>15</sup>        | 600 - 1000                 | 30 s                     | Diffusion tail develops above 900°C. [7]                                                    |

| Helium        | 230          | 5 x 10 <sup>16</sup>        | 1000                       | 30 min                   | Rod-like defects diminished, tangled dislocations and large dislocation loops appeared. [8] |

| Aluminum      | 80           | 1 x 10 <sup>14</sup>        | 1200                       | 1 h (in O <sub>2</sub> ) | Enhanced formation of dislocations and oxidation-induced stacking faults. [3]               |

| Indium        | 1000         | 1.5 x 10 <sup>13</sup>      | 900                        | 5 s - 15 min             | Dislocation rods form and can be unstable at longer anneal                                  |

times for

lower doses.

[9]

Table 2: Electrical Activation and Defect Evolution Temperatures

| Temperature Range (°C) | Phenomenon                                   | Impact on Silicon                                         |

|------------------------|----------------------------------------------|-----------------------------------------------------------|

| Up to 500              | Recombination of vacancies and interstitials | Removes trapping defects, releasing carriers.[1]          |

| 500 - 600              | Formation of dislocations                    | Decreases electrical activity due to impurity capture.[1] |

| 500 - 600              | Solid-phase epitaxy                          | Recrystallization of amorphous layers.[1]                 |

| 800 - 1000             | Peak electrical activation                   | Dopants occupy substitutional sites.[1]                   |

| 900 - 1000             | Dissolution of dislocations                  | Reduces defect density.[1]                                |

## Experimental Protocols

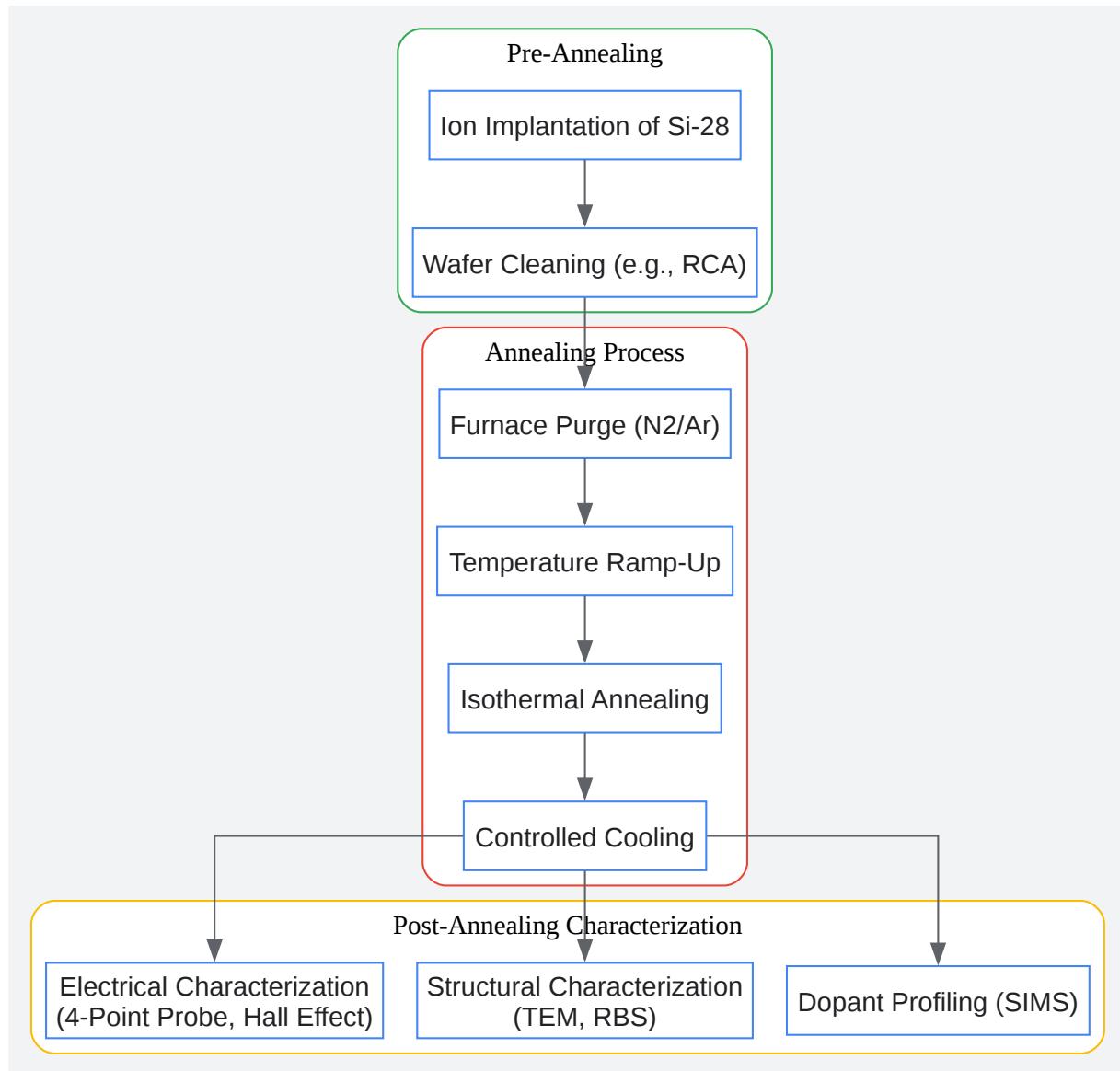

### Detailed Methodology: Furnace Annealing of Ion-Implanted Silicon-28

This protocol provides a general framework. Specific parameters should be optimized for your particular dopant, implant energy, and dose.

- Sample Preparation:

- Begin with a clean, ion-implanted Silicon-28 wafer.

- Ensure the wafer is free of organic and particulate contamination by performing a standard cleaning procedure (e.g., RCA clean).

- Furnace Setup:

- Use a high-temperature tube furnace capable of reaching at least 1200°C.

- The furnace tube should be made of a high-purity material like quartz.

- Establish a controlled, inert atmosphere by purging the furnace tube with high-purity nitrogen (N<sub>2</sub>) or argon (Ar) gas. A typical flow rate is several standard liters per minute (slm).<sup>[5]</sup>

- Annealing Process:

- Loading: Carefully load the wafer into the center of the furnace tube using a clean quartz boat.

- Ramping: Ramp the furnace temperature to the desired annealing temperature at a controlled rate. A typical ramp rate is 5-10°C per minute.

- Soaking: Hold the wafer at the target annealing temperature (e.g., 900-1100°C) for the specified duration (e.g., 30 minutes).

- Cooling: After the soak time, cool the furnace down to room temperature at a controlled rate.

- Post-Annealing Characterization:

- Remove the wafer from the furnace.

- Characterize the electrical properties (e.g., sheet resistance, carrier concentration) using techniques like four-point probe measurements or Hall effect measurements.

- Analyze the crystal structure and defect distribution using methods such as Transmission Electron Microscopy (TEM) or Rutherford Backscattering Spectrometry (RBS).

- Evaluate the dopant profile using Secondary Ion Mass Spectrometry (SIMS).

## Visualizations

[Click to download full resolution via product page](#)

Caption: Experimental workflow for annealing ion-implanted Si-28.

[Click to download full resolution via product page](#)

Caption: Troubleshooting logic for common annealing issues.

#### Need Custom Synthesis?

BenchChem offers custom synthesis for rare earth carbides and specific isotopic labeling.

Email: [info@benchchem.com](mailto:info@benchchem.com) or [Request Quote Online](#).

## References

- 1. [eesemi.com](http://eesemi.com) [eesemi.com]

- 2. "Implant Annealing of Al Dopants in Silicon Carbide using Silane Overpr" by Shailaja P. Rao [digitalcommons.usf.edu]

- 3. [iitg.ac.in](http://iitg.ac.in) [iitg.ac.in]

- 4. [axcelis.com](http://axcelis.com) [axcelis.com]

- 5. [lab.semi.ac.cn](http://lab.semi.ac.cn) [lab.semi.ac.cn]

- 6. [researchgate.net](http://researchgate.net) [researchgate.net]

- 7. [pubs.aip.org](http://pubs.aip.org) [pubs.aip.org]

- 8. Microstructure Evolution in He-Implanted Si at 600 °C Followed by 1000 °C Annealing - PMC [pmc.ncbi.nlm.nih.gov]

- 9. ir.amolf.nl [ir.amolf.nl]

- To cite this document: BenchChem. [Technical Support Center: Optimizing Annealing Processes for Ion-Implanted Silicon-28]. BenchChem, [2025]. [Online PDF]. Available at: [https://www.benchchem.com/product/b1172460#optimizing-annealing-processes-for-ion-implanted-silicon-28]

**Disclaimer & Data Validity:**

The information provided in this document is for Research Use Only (RUO) and is strictly not intended for diagnostic or therapeutic procedures. While BenchChem strives to provide accurate protocols, we make no warranties, express or implied, regarding the fitness of this product for every specific experimental setup.

**Technical Support:** The protocols provided are for reference purposes. Unsure if this reagent suits your experiment? [\[Contact our Ph.D. Support Team for a compatibility check\]](#)

**Need Industrial/Bulk Grade?** [Request Custom Synthesis Quote](#)

## BenchChem

Our mission is to be the trusted global source of essential and advanced chemicals, empowering scientists and researchers to drive progress in science and industry.

### Contact

Address: 3281 E Guasti Rd

Ontario, CA 91761, United States

Phone: (601) 213-4426

Email: [info@benchchem.com](mailto:info@benchchem.com)