# In<sub>2</sub>Se<sub>3</sub> vs. Silicon: A Comparative Guide for Low-Power Computing

**Author:** BenchChem Technical Support Team. **Date:** December 2025

## Compound of Interest

Compound Name: Indium selenide (In<sub>2</sub>Se<sub>3</sub>)

Cat. No.: B1172673

[Get Quote](#)

For Researchers, Scientists, and Drug Development Professionals

The relentless pursuit of computational power, intertwined with the escalating energy demands of modern computing, has catalyzed the search for alternatives to silicon-based electronics. As silicon CMOS technology approaches its fundamental scaling limits, emerging materials like Indium Selenide (In<sub>2</sub>Se<sub>3</sub>) are being explored for their potential to enable the next generation of low-power computing devices. This guide provides an objective comparison of the performance of In<sub>2</sub>Se<sub>3</sub> and silicon, supported by experimental data, to inform researchers and professionals in computationally intensive fields.

## At a Glance: Key Performance Metrics

The suitability of a material for low-power computing is determined by a combination of factors that govern its efficiency, speed, and scalability. Below is a summary of key performance metrics for transistors based on  $\alpha$ -In<sub>2</sub>Se<sub>3</sub>, a ferroelectric phase of Indium Selenide, and state-of-the-art silicon FinFETs. It is important to note that the values for In<sub>2</sub>Se<sub>3</sub> are derived from various research reports and may not represent optimized, production-level devices, while silicon values reflect a mature, highly-developed technology.

| Performance Metric          | $\alpha\text{-In}_2\text{Se}_3$ Field-Effect Transistors (Fe-FETs)                      | Silicon FinFETs (7nm node)       | Significance for Low-Power Computing                                                                           |

|-----------------------------|-----------------------------------------------------------------------------------------|----------------------------------|----------------------------------------------------------------------------------------------------------------|

| On/Off Current Ratio        | $> 10^8$ <sup>[1]</sup>                                                                 | $> 10^5$                         | A high ratio is crucial for distinguishing between the 'on' and 'off' states, minimizing leakage power.        |

| Subthreshold Swing (SS)     | As low as 10 mV/dec (in mixed-dimensional JFETs)                                        | ~60 mV/dec (at room temperature) | A lower SS allows for a lower threshold voltage and reduced power consumption.                                 |

| Carrier Mobility (Electron) | 19.3 - 1185 cm <sup>2</sup> /V·s <sup>[1]</sup>                                         | ~1400 cm <sup>2</sup> /V·s       | Higher mobility contributes to faster switching speeds and higher performance.                                 |

| Operating Voltage           | Can be significantly reduced compared to SiO <sub>2</sub> -based devices <sup>[1]</sup> | ~0.7 V                           | Lower operating voltages directly translate to reduced dynamic power consumption.                              |

| Non-volatility              | Yes (due to ferroelectricity) <sup>[2]</sup>                                            | No                               | The ability to retain its state without power can lead to novel low-power "in-memory" computing architectures. |

## The Ferroelectric Advantage of In<sub>2</sub>Se<sub>3</sub>

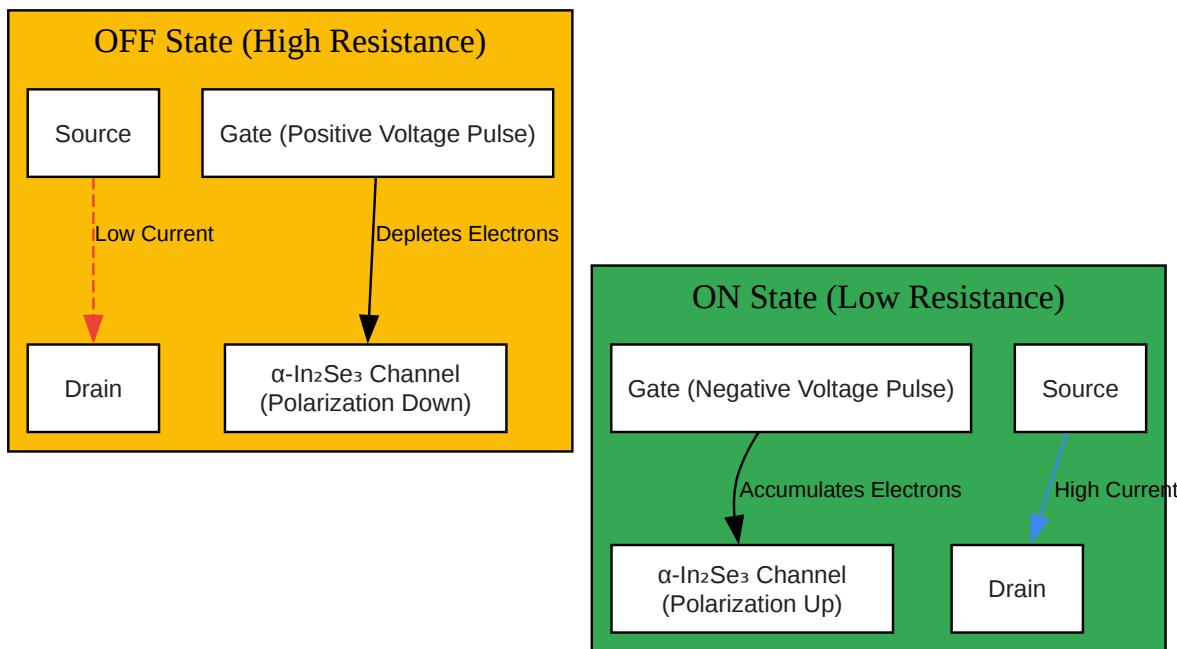

The key differentiator for In<sub>2</sub>Se<sub>3</sub> in the context of low-power computing is its intrinsic ferroelectricity. In conventional silicon transistors, a continuous voltage must be applied to the gate to maintain the 'on' state, leading to static power consumption. In contrast, the ferroelectric nature of  $\alpha\text{-In}_2\text{Se}_3$  allows for the non-volatile storage of a polarization state. This means that

once the transistor is switched 'on' or 'off' by an electric field, it retains that state even when the power is removed. This property opens the door to novel computing paradigms such as logic-in-memory, where computation and data storage are co-located, significantly reducing the energy-intensive process of data shuttling.

The working principle of an  $\alpha\text{-In}_2\text{Se}_3$  ferroelectric field-effect transistor (Fe-FET) is illustrated below. The direction of the ferroelectric polarization in the  $\text{In}_2\text{Se}_3$  channel modulates the charge carrier concentration, thereby switching the transistor between a high-resistance ('off') and a low-resistance ('on') state.

[Click to download full resolution via product page](#)

Figure 1: Principle of an  $\alpha\text{-In}_2\text{Se}_3$  ferroelectric transistor.

## Experimental Protocols

Accurate comparison of materials requires standardized experimental procedures. Below are generalized protocols for the fabrication and characterization of  $\alpha\text{-In}_2\text{Se}_3$  Fe-FETs and silicon FinFETs, based on common practices in the field.

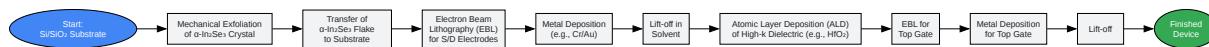

# Fabrication of a Top-Gated $\alpha$ -In<sub>2</sub>Se<sub>3</sub> Ferroelectric Field-Effect Transistor

This protocol outlines the typical steps for creating a laboratory-scale  $\alpha$ -In<sub>2</sub>Se<sub>3</sub> transistor.

[Click to download full resolution via product page](#)

Figure 2: Fabrication workflow for an  $\alpha$ -In<sub>2</sub>Se<sub>3</sub> Fe-FET.

- Substrate Preparation: A heavily doped silicon wafer with a thermally grown silicon dioxide (SiO<sub>2</sub>) layer is used as the back gate and gate dielectric, respectively.

- Material Exfoliation and Transfer: Thin flakes of  $\alpha$ -In<sub>2</sub>Se<sub>3</sub> are mechanically exfoliated from a bulk crystal using adhesive tape. These flakes are then transferred onto the Si/SiO<sub>2</sub> substrate.

- Source and Drain Electrode Patterning: Standard electron beam lithography (EBL) is used to define the source and drain contact regions.

- Metal Deposition: A metal stack, typically Cr/Au or Ti/Au, is deposited using electron beam evaporation.

- Lift-off: The sample is immersed in a solvent to lift off the unpatterned metal, leaving the source and drain electrodes.

- Top Gate Dielectric Deposition: A high-k dielectric material, such as hafnium oxide (HfO<sub>2</sub>), is deposited via atomic layer deposition (ALD) to serve as the top gate insulator.

- Top Gate Electrode Patterning and Deposition: A second EBL and metal deposition step is performed to define the top gate electrode.

- Final Lift-off: A final lift-off process completes the device fabrication.

## Characterization of a Silicon FinFET

The characterization of a silicon FinFET involves a series of electrical measurements to determine its key performance parameters.

- Device Preparation: A fabricated FinFET on a silicon-on-insulator (SOI) wafer is used. The device dimensions, such as fin width, fin height, and gate length, are critical parameters.

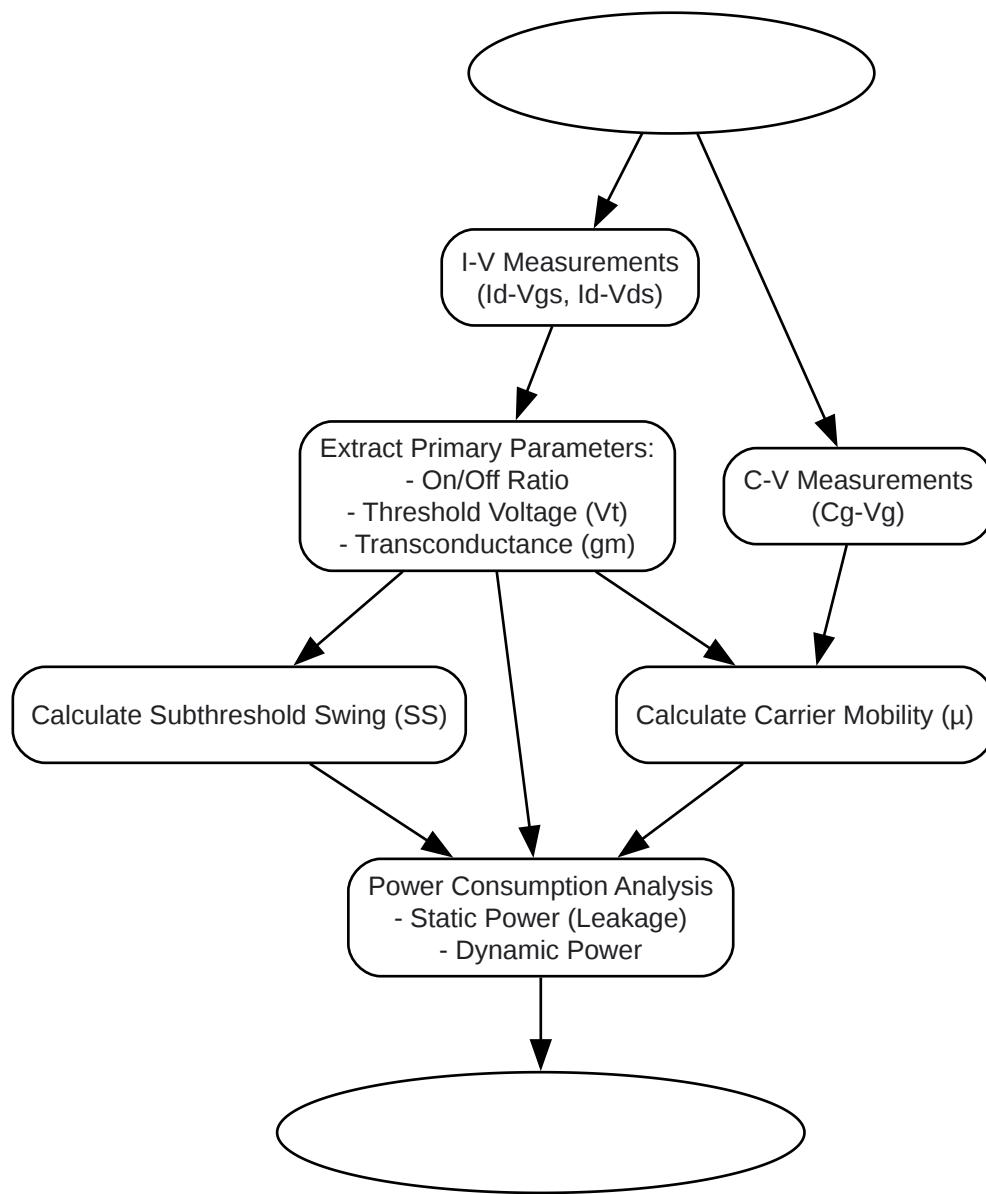

- I-V Characterization:

- Transfer Characteristics ( $Id$ - $Vgs$ ): The drain current ( $Id$ ) is measured as the gate-source voltage ( $Vgs$ ) is swept at a constant drain-source voltage ( $Vds$ ). This measurement is used to determine the on/off ratio, subthreshold swing, and threshold voltage.

- Output Characteristics ( $Id$ - $Vds$ ): The drain current is measured as  $Vds$  is swept for different constant values of  $Vgs$ . This provides information about the transistor's output resistance and saturation behavior.

- Capacitance-Voltage (C-V) Measurement: The gate capacitance is measured as a function of the gate voltage. This data is used to extract parameters like the gate oxide thickness and to calculate the carrier mobility.

- Mobility Extraction: The field-effect mobility is calculated from the transconductance ( $gm$ ), which is derived from the  $Id$ - $Vgs$  curve, and the gate capacitance obtained from C-V measurements.

- Power Consumption Analysis:

- Static Power: Measured when the transistor is in a steady 'on' or 'off' state. It is primarily due to leakage currents.

- Dynamic Power: Measured during switching. It is a function of the switching frequency, supply voltage, and load capacitance.

## Logical Flow of Transistor Characterization

The process of characterizing a transistor, whether it is based on  $In_2Se_3$  or silicon, follows a logical progression from basic current-voltage measurements to the extraction of key

performance metrics.

[Click to download full resolution via product page](#)

Figure 3: Logical workflow for transistor characterization.

## Conclusion and Future Outlook

Indium Selenide, particularly in its ferroelectric  $\alpha$ -phase, presents a compelling case as a potential successor to silicon for certain low-power computing applications. Its non-volatile nature offers a distinct advantage for in-memory computing and reducing static power

consumption. However, significant challenges remain in terms of large-scale, uniform material synthesis and device fabrication, as well as long-term stability and reliability.

Silicon FinFET technology, on the other hand, is a mature and highly optimized platform that continues to evolve. While facing fundamental physical limitations, innovations in device architecture and materials integration are extending its lifespan.

For researchers and professionals in fields demanding high-performance and energy-efficient computing, the development of  $\text{In}_2\text{Se}_3$  and other 2D materials warrants close attention. While direct replacement of silicon in all applications is unlikely in the near term,  $\text{In}_2\text{Se}_3$ -based devices could find application in specialized, low-power domains and next-generation computing architectures that leverage their unique ferroelectric properties. Continued research and direct, standardized benchmarking against silicon will be crucial to fully assess the potential of  $\text{In}_2\text{Se}_3$  to help redefine the landscape of low-power electronics.

#### Need Custom Synthesis?

BenchChem offers custom synthesis for rare earth carbides and specific isotopic labeling.

Email: [info@benchchem.com](mailto:info@benchchem.com) or [Request Quote Online](#).

## References

- 1. [engineering.purdue.edu](http://engineering.purdue.edu) [engineering.purdue.edu]

- 2. [staff.ustc.edu.cn](http://staff.ustc.edu.cn) [staff.ustc.edu.cn]

- To cite this document: BenchChem. [ $\text{In}_2\text{Se}_3$  vs. Silicon: A Comparative Guide for Low-Power Computing]. BenchChem, [2025]. [Online PDF]. Available at: <https://www.benchchem.com/product/b1172673#in-se-vs-silicon-for-low-power-computing-devices>

#### Disclaimer & Data Validity:

The information provided in this document is for Research Use Only (RUO) and is strictly not intended for diagnostic or therapeutic procedures. While BenchChem strives to provide accurate protocols, we make no warranties, express or implied, regarding the fitness of this product for every specific experimental setup.

**Technical Support:** The protocols provided are for reference purposes. Unsure if this reagent suits your experiment? [\[Contact our Ph.D. Support Team for a compatibility check\]](#)

**Need Industrial/Bulk Grade?** [Request Custom Synthesis Quote](#)

## BenchChem

Our mission is to be the trusted global source of essential and advanced chemicals, empowering scientists and researchers to drive progress in science and industry.

### Contact

Address: 3281 E Guasti Rd

Ontario, CA 91761, United States

Phone: (601) 213-4426

Email: [info@benchchem.com](mailto:info@benchchem.com)