# Naphthacene Films: Technical Support Center for Enhanced Charge Carrier Mobility

**Author:** BenchChem Technical Support Team. **Date:** December 2025

## Compound of Interest

Compound Name: **Naphthacene**

Cat. No.: **B114907**

[Get Quote](#)

This technical support center provides researchers, scientists, and drug development professionals with comprehensive troubleshooting guides and frequently asked questions (FAQs) to address common challenges in improving the charge carrier mobility of **naphthacene** thin films.

## Troubleshooting Guide & FAQs

This section addresses specific issues encountered during the fabrication and characterization of **naphthacene**-based thin-film transistors (TFTs), with a focus on resolving low charge carrier mobility.

### Issue 1: Low Charge Carrier Mobility

**Q:** My fabricated **naphthacene** TFT exhibits significantly lower charge carrier mobility than expected. What are the potential causes and how can I improve it?

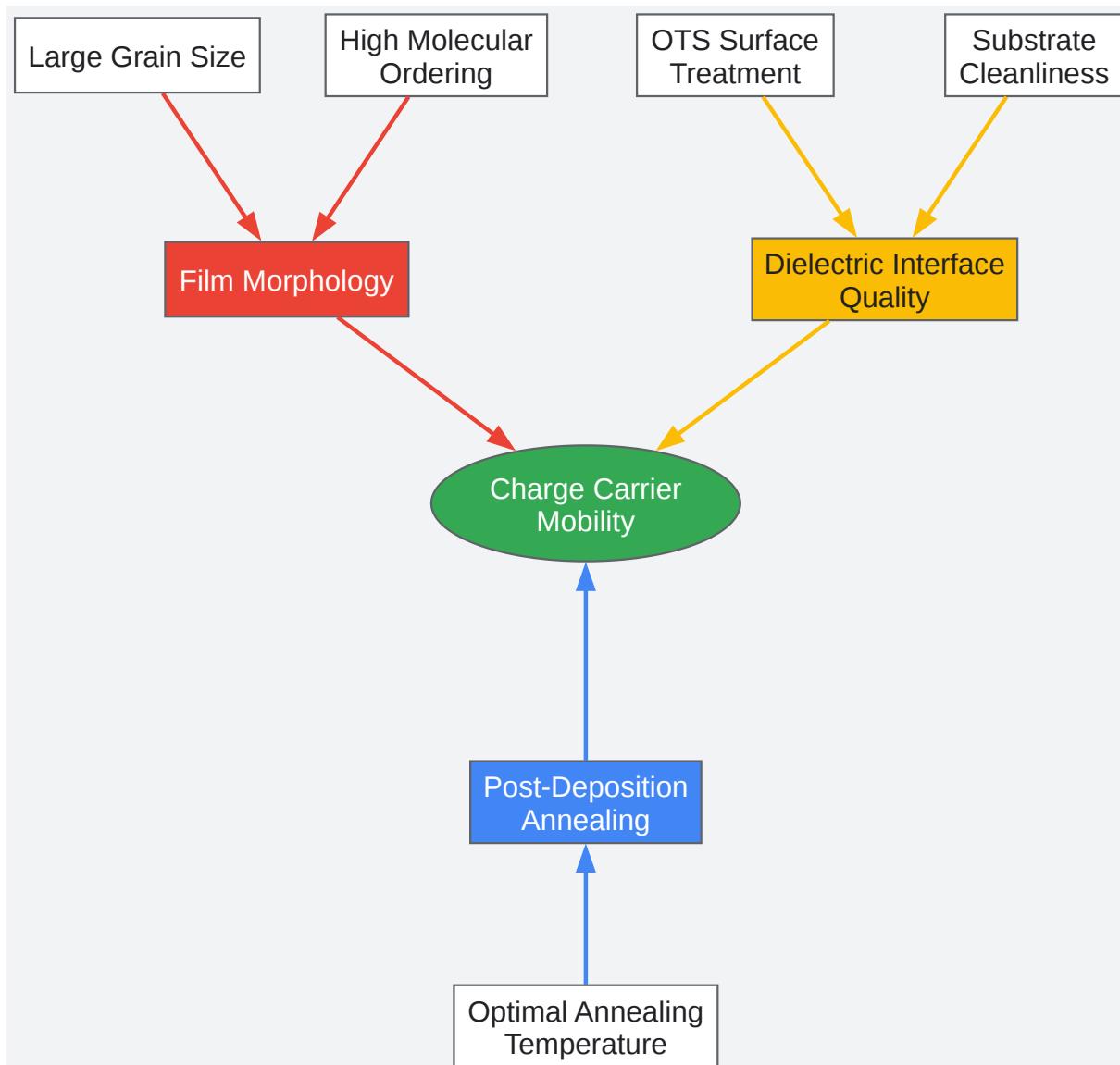

**A:** Low charge carrier mobility in **naphthacene** TFTs is a common issue that can stem from several factors, primarily related to the quality of the semiconductor film and the device interfaces. The key areas to investigate are film morphology, dielectric surface preparation, and post-deposition processing.

- **Poor Film Morphology:** The arrangement of **naphthacene** molecules into well-ordered crystalline domains is crucial for efficient charge transport. Small grain sizes and a high

density of grain boundaries act as trapping sites for charge carriers, thereby reducing mobility.

- Troubleshooting Steps:

- Analyze Film Morphology: Use Atomic Force Microscopy (AFM) to visualize the surface morphology of your **naphthacene** film. Look for large, interconnected crystalline grains. Small, isolated grains are indicative of a suboptimal deposition process.

- Optimize Deposition Parameters:

- Substrate Temperature: The temperature of the substrate during thermal evaporation significantly influences film growth. A systematic variation of the substrate temperature (e.g., from room temperature to 100°C) should be performed to find the optimal conditions for promoting large grain formation.

- Deposition Rate: A lower deposition rate (e.g., 0.1-0.5 Å/s) generally allows more time for molecules to arrange themselves into ordered structures, leading to improved crystallinity.

- Inadequate Dielectric Surface: The interface between the gate dielectric and the **naphthacene** film is where charge transport occurs. A rough or contaminated surface can introduce charge traps and hinder mobility.

- Troubleshooting Steps:

- Substrate Cleaning: Ensure a rigorous cleaning procedure for your substrate (e.g., silicon wafer with silicon dioxide) to remove any organic or particulate contamination. A typical procedure involves sequential sonication in acetone and isopropanol, followed by drying with nitrogen and a UV-ozone treatment.

- Surface Treatment with Self-Assembled Monolayers (SAMs): Treating the  $\text{SiO}_2$  surface with a SAM like octadecyltrichlorosilane (OTS) is a highly effective method to improve mobility. OTS treatment reduces surface energy, promoting better molecular ordering of the **naphthacene** film and passivating charge trapping sites (e.g., Si-OH groups) on the  $\text{SiO}_2$  surface.

- Suboptimal Post-Deposition Processing:

- Troubleshooting Steps:

- Thermal Annealing: Post-deposition annealing of the **naphthacene** film can enhance its crystallinity and, consequently, the charge carrier mobility. However, the annealing temperature is a critical parameter. For some organic semiconductors like pentacene, annealing at temperatures around 45°C has been shown to improve mobility, while higher temperatures can be detrimental. It is crucial to perform a systematic study of the annealing temperature and duration for your specific **naphthacene** films. Annealing should be carried out in an inert atmosphere (e.g., a nitrogen-filled glovebox) to prevent degradation of the organic material.

#### Issue 2: High OFF-Current in TFTs

Q: My **naphthacene** TFT shows a high OFF-current, leading to a low ON/OFF ratio. What could be the cause and how can I reduce it?

A: A high OFF-current can be attributed to several factors, including leakage currents through the gate dielectric and a poorly formed semiconductor film.

- Troubleshooting Steps:

- Inspect Gate Dielectric Quality: A thin and pinhole-free gate dielectric is essential to prevent gate leakage current. Ensure the quality of your thermally grown SiO<sub>2</sub> or other dielectric material.

- Improve Film Morphology: A discontinuous **naphthacene** film can create leakage pathways between the source and drain electrodes. Optimizing the deposition parameters to achieve a uniform and continuous film is crucial.

- Dielectric Surface Passivation: As mentioned for improving mobility, treating the dielectric surface with an OTS monolayer can help in passivating trap states that might contribute to leakage currents.

## Quantitative Data on Factors Influencing Mobility

The following tables summarize the impact of various experimental parameters on the charge carrier mobility of organic semiconductor films. Note that while the focus is on **naphthacene**, some data from the closely related and well-studied pentacene is included for comparative purposes, as the underlying principles are often similar.

Table 1: Effect of Post-Deposition Annealing on Charge Carrier Mobility

| Organic Semiconductor | Annealing Temperature (°C) | Annealing Duration | Initial Mobility (cm <sup>2</sup> /Vs) | Mobility after Annealing (cm <sup>2</sup> /Vs) | Reference |

|-----------------------|----------------------------|--------------------|----------------------------------------|------------------------------------------------|-----------|

| Naphthacene           | 90                         | 5 hours            | -                                      | 0.07 x 10 <sup>-3</sup>                        | [1]       |

| Pentacene             | 45                         | -                  | -                                      | Improved                                       | [2]       |

| Pentacene             | >50                        | -                  | -                                      | Decreased                                      | [2]       |

| Pentacene             | 150                        | 15 hours           | -                                      | Increased by ~30%                              | [2]       |

Table 2: Influence of Dielectric Surface Treatment on Mobility in Pentacene TFTs

| Surface Treatment            | Mobility (cm <sup>2</sup> /Vs) | On/Off Ratio     | Reference |

|------------------------------|--------------------------------|------------------|-----------|

| Bare SiO <sub>2</sub>        | ~0.1                           | ~10 <sup>4</sup> | [3]       |

| OTS-treated SiO <sub>2</sub> | ~0.15                          | ~10 <sup>5</sup> | [3]       |

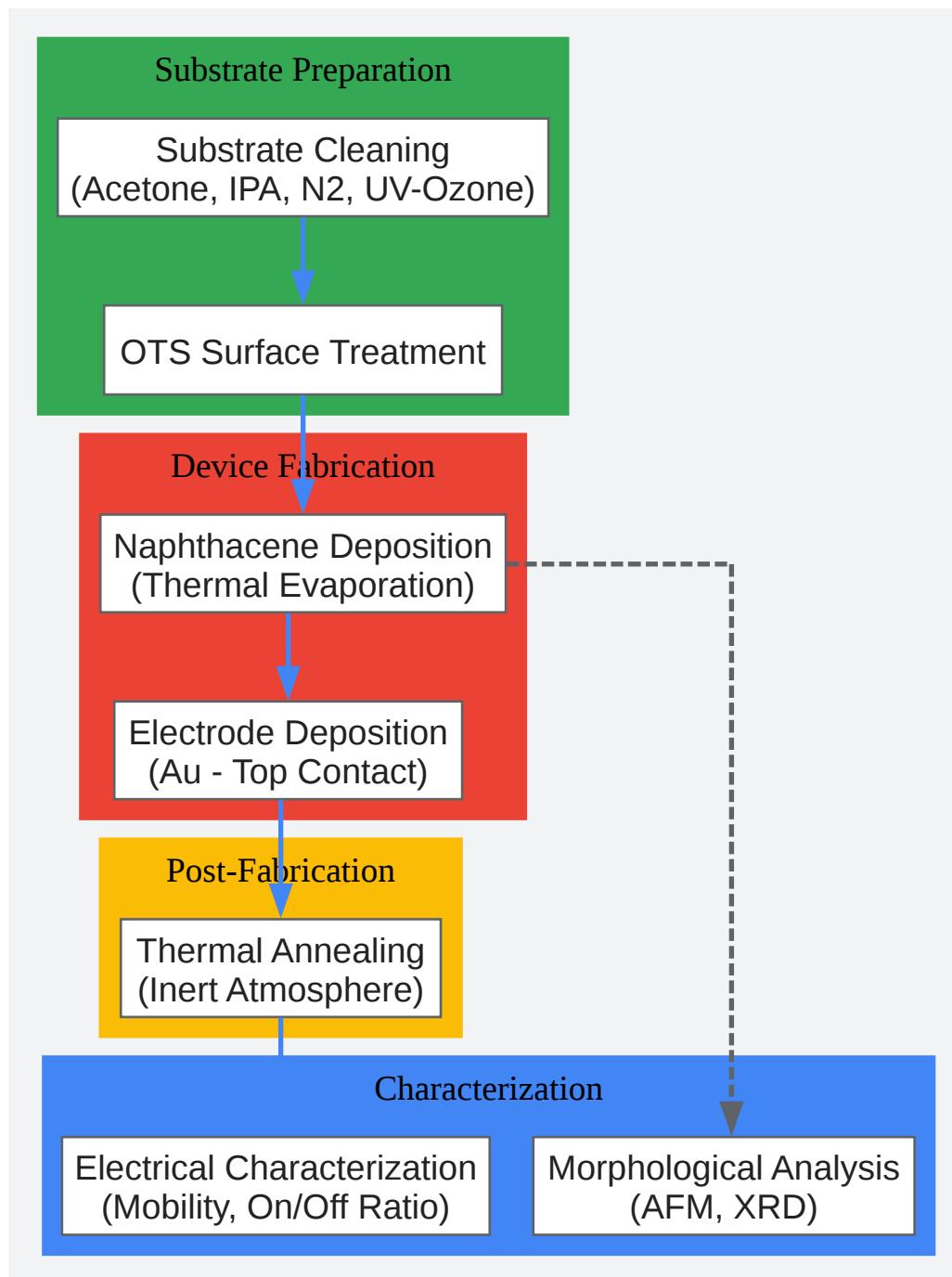

## Experimental Protocols

This section provides detailed methodologies for key experiments to improve the charge carrier mobility in **naphthacene** films.

### Protocol 1: Octadecyltrichlorosilane (OTS) Treatment of SiO<sub>2</sub>/Si Substrates

- Substrate Cleaning:

- Sequentially sonicate the SiO<sub>2</sub>/Si substrates in acetone and then isopropanol for 15 minutes each.

- Dry the substrates with a stream of high-purity nitrogen gas.

- Treat the substrates with UV-ozone for 10-15 minutes to remove any residual organic contaminants and to create a hydrophilic surface.

- OTS Solution Preparation:

- In a nitrogen-filled glovebox, prepare a dilute solution of OTS in an anhydrous solvent such as toluene or hexadecane. A typical concentration is in the range of 1-10 mM.

- OTS Monolayer Deposition:

- Immerse the cleaned and dried substrates in the OTS solution for a specified duration, typically ranging from 30 minutes to several hours. The deposition is usually carried out at room temperature.

- Rinsing and Curing:

- After immersion, rinse the substrates thoroughly with the pure solvent (toluene or hexadecane) to remove any physisorbed OTS molecules.

- Subsequently, rinse with isopropanol and dry with nitrogen.

- Cure the OTS-treated substrates by annealing them on a hotplate at a temperature of 100-120°C for 1 hour. This step helps to form a well-ordered and covalently bonded monolayer.

- Verification of Surface Treatment:

- The success of the OTS treatment can be verified by measuring the water contact angle on the surface. A hydrophobic surface with a contact angle greater than 100° is indicative of a well-formed OTS monolayer.

## Protocol 2: Thermal Evaporation of **Naphthacene** Thin Films

- Substrate Preparation:

- Use cleaned and, if desired, OTS-treated SiO<sub>2</sub>/Si substrates.

- Mount the substrates onto the substrate holder in the thermal evaporation chamber.

- Source Material Preparation:

- Place high-purity **naphthacene** powder in a suitable evaporation source, such as a quartz crucible or a molybdenum boat.

- Vacuum Deposition:

- Evacuate the chamber to a high vacuum, typically in the range of 10<sup>-6</sup> to 10<sup>-7</sup> Torr, to ensure a long mean free path for the evaporated molecules and to minimize contamination.

- Heat the substrate to the desired temperature using a substrate heater.

- Gradually increase the current to the evaporation source to heat the **naphthacene** until it starts to sublime.

- Control the deposition rate using a quartz crystal microbalance. A slow deposition rate (e.g., 0.2 Å/s) is generally preferred for achieving higher crystallinity.

- Deposit a **naphthacene** film of the desired thickness, typically in the range of 30-50 nm for TFT applications.

- Device Completion:

- After the **naphthacene** deposition, without breaking the vacuum, deposit the source and drain electrodes (e.g., gold) through a shadow mask. This top-contact configuration is often preferred to minimize contact resistance.

#### Protocol 3: Post-Deposition Annealing of **Naphthacene** Films

- Inert Atmosphere:

- Transfer the fabricated devices into a nitrogen-filled glovebox to prevent exposure to oxygen and moisture, which can degrade the performance of the organic semiconductor.

- Thermal Annealing:

- Place the devices on a hotplate inside the glovebox.

- Heat the devices to the desired annealing temperature for a specific duration. A systematic study is recommended to find the optimal conditions. For example, you can anneal different samples at temperatures ranging from 60°C to 120°C for 30-60 minutes.

- Cooling:

- After annealing, allow the devices to cool down slowly to room temperature before performing electrical characterization.

## Visualizations

The following diagrams illustrate key workflows and relationships in the fabrication of high-mobility **naphthacene** TFTs.

[Click to download full resolution via product page](#)

Caption: Experimental workflow for fabricating high-mobility **naphthacene** TFTs.

[Click to download full resolution via product page](#)

Caption: Key factors influencing charge carrier mobility in **naphthacene** films.

#### Need Custom Synthesis?

BenchChem offers custom synthesis for rare earth carbides and specific isotopic labeling.

Email: [info@benchchem.com](mailto:info@benchchem.com) or [Request Quote Online](#).

## References

- 1. researchgate.net [researchgate.net]

- 2. Advances in Charge Carrier Mobility of Diketopyrrolopyrrole-Based Organic Semiconductors [mdpi.com]

- 3. Excited-State Aromaticity Reversals in Naphthalene and Anthracene - PMC [pmc.ncbi.nlm.nih.gov]

- To cite this document: BenchChem. [Naphthacene Films: Technical Support Center for Enhanced Charge Carrier Mobility]. BenchChem, [2025]. [Online PDF]. Available at: [https://www.benchchem.com/product/b114907#improving-charge-carrier-mobility-in-naphthacene-films]

### Disclaimer & Data Validity:

The information provided in this document is for Research Use Only (RUO) and is strictly not intended for diagnostic or therapeutic procedures. While BenchChem strives to provide accurate protocols, we make no warranties, express or implied, regarding the fitness of this product for every specific experimental setup.

**Technical Support:** The protocols provided are for reference purposes. Unsure if this reagent suits your experiment? [\[Contact our Ph.D. Support Team for a compatibility check\]](#)

**Need Industrial/Bulk Grade?** [Request Custom Synthesis Quote](#)

## BenchChem

Our mission is to be the trusted global source of essential and advanced chemicals, empowering scientists and researchers to drive progress in science and industry.

### Contact

Address: 3281 E Guasti Rd

Ontario, CA 91761, United States

Phone: (601) 213-4426

Email: [info@benchchem.com](mailto:info@benchchem.com)