# Technical Support Center: Scaling Hafnium Oxide-Based Memory Devices

**Author:** BenchChem Technical Support Team. **Date:** January 2026

## Compound of Interest

Compound Name: *Hafnium oxide*

Cat. No.: *B10860814*

[Get Quote](#)

Welcome to the technical support resource for researchers and scientists navigating the complexities of **hafnium oxide** ( $\text{HfO}_2$ ) based memory devices. This guide is designed to address the specific, practical challenges encountered during the fabrication, characterization, and scaling of these promising non-volatile memory technologies. Instead of a generic overview, we will dive directly into a question-and-answer format to troubleshoot common experimental hurdles, grounded in field-proven insights and authoritative references.

## Section 1: Fabrication and Material-Related Issues

This section addresses common problems that arise from the synthesis and processing of the ferroelectric  $\text{HfO}_2$  thin film, which are foundational to device performance.

### Q1: My as-deposited $\text{HfO}_2$ films are not ferroelectric. The P-E hysteresis loop is linear. What is the primary cause?

A1: The ferroelectric phase in **hafnium oxide**, the non-centrosymmetric orthorhombic phase (o-phase,  $\text{Pca}2_1$ ), is metastable and typically does not form in as-deposited films.<sup>[1]</sup> Your films are likely in the amorphous or the thermodynamically stable monoclinic (m-phase) state, both of which are non-ferroelectric.

Causality & Troubleshooting:

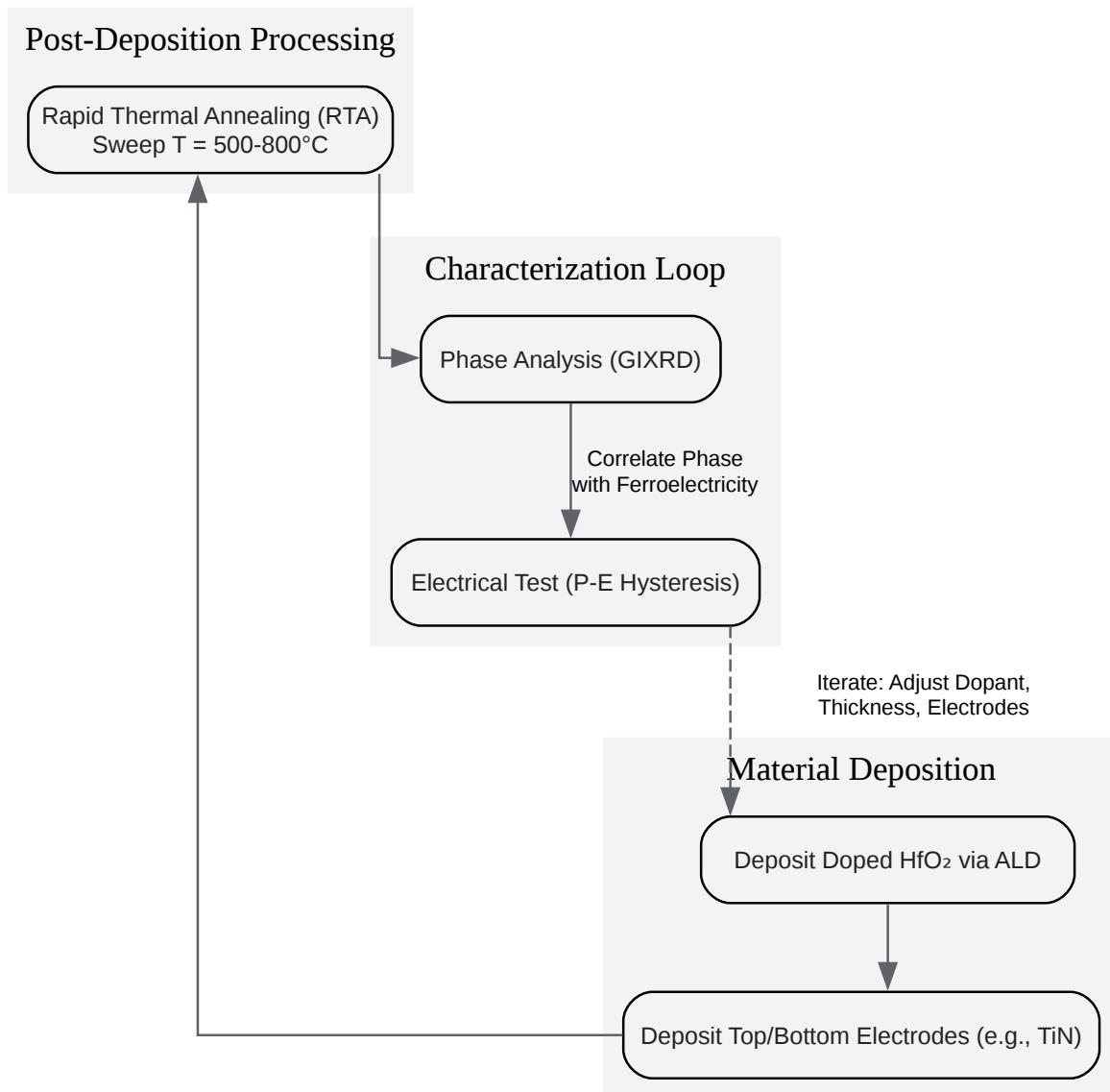

- Crystallization is Required: Ferroelectricity in  $\text{HfO}_2$  is contingent upon crystallization into the correct polymorphic phase. This is almost always achieved through a post-deposition

annealing step.[2]

- Annealing Temperature is Critical: The temperature window for stabilizing the o-phase is narrow.

- Too Low: The film may remain amorphous or have incomplete crystallization, resulting in no ferroelectricity. Crystallization temperatures for doped  $\text{HfO}_2$  are typically in the range of 450-550°C.[1]

- Too High: Annealing at excessively high temperatures (e.g., >900°C for some doped variants) provides enough energy for the film to relax into the more stable, non-ferroelectric monoclinic phase, which will extinguish the ferroelectric behavior.[1][3]

- Actionable Steps:

- Implement a rapid thermal annealing (RTA) step after top electrode deposition.

- Systematically vary the annealing temperature (e.g., from 500°C to 800°C in 50°C increments) to find the optimal window for your specific film thickness, dopant, and substrate.[4]

- Characterize the crystalline phase post-annealing using Grazing Incidence X-ray Diffraction (GIXRD) to correlate thermal budget with phase formation.

## **Q2: I've achieved ferroelectricity, but the remnant polarization ( $P_r$ ) is low and the coercive field ( $E_e$ ) is very high. How can I improve the hysteresis loop?**

A2: A suboptimal hysteresis loop with low  $P_r$  and high  $E_e$  suggests that either the ferroelectric phase is not dominant, or there are significant pinning effects from defects and grain boundaries. Several factors, including dopants, film thickness, and electrode interfaces, govern these properties.

Causality & Troubleshooting:

- Dopant and Concentration: Dopants like Si, Al, Zr, Gd, and La are used to stabilize the ferroelectric o-phase by disrupting the formation of the monoclinic phase.[5] The type and

concentration of the dopant are critical. For instance, La-doping can induce a[6] texture which improves  $P_r$  and reduces the wake-up effect.[5]

- Electrode and Interface Engineering: The interface between the  $HfO_2$  and the electrode is crucial. A poor interface can lead to defect formation (especially oxygen vacancies) and charge trapping, which can pin domains and increase the coercive field.[7] Using nitrogen-rich TiN electrodes has been shown to improve endurance by reducing the formation of defects at the interface.[5]

- Mechanical Stress: Stress, induced by the substrate and electrodes due to thermal expansion mismatch, can significantly influence phase stability.[1] This is a key reason why the choice of substrate and electrode material impacts performance.

#### Experimental Protocol Workflow: Optimizing $HfO_2$ Ferroelectricity

[Click to download full resolution via product page](#)

Caption: Workflow for optimizing  $\text{HfO}_2$  ferroelectric properties.

## Section 2: Device Performance and Reliability Issues

This section troubleshoots common degradation phenomena observed during the electrical cycling and testing of  $\text{HfO}_2$  memory devices.

## Q3: My device exhibits a strong "wake-up" effect, where $P_r$ increases significantly over the first $10^4$ - $10^6$ cycles. Why does this happen and is it a reliability concern?

A3: The wake-up effect is a hallmark of many  $\text{HfO}_2$ -based ferroelectric devices. It is characterized by an initial increase in remnant polarization with electrical cycling.<sup>[6]</sup> While it can lead to the desired high- $P_r$  state, it represents an initial instability that must be understood and controlled for reliable device operation.

Causality & Troubleshooting:

- Phase Transition: One prominent theory is that the wake-up effect corresponds to an electric-field-driven phase transition from a non-ferroelectric (e.g., tetragonal) to the ferroelectric orthorhombic phase.<sup>[8]</sup> Synchrotron X-ray diffraction studies have observed this phase exchange during cycling.<sup>[8]</sup>

- Defect Redistribution: The high electric fields during cycling can cause the migration of defects, particularly oxygen vacancies.<sup>[9][10]</sup> The movement of these charged defects away from domain walls or interfaces can "unpin" ferroelectric domains, allowing them to switch more easily and contribute to a larger net polarization.<sup>[11]</sup>

- Domain Depinning: In the pristine state, some ferroelectric domains may be pinned by local defects or grain boundaries. Cycling provides the energy to overcome these local barriers, freeing more domains to participate in switching.<sup>[11]</sup>

Mitigation Strategies:

- Annealing Optimization: Devices annealed at higher temperatures (within the ferroelectric window) often show a less pronounced wake-up effect, suggesting a more complete initial transformation to the o-phase.<sup>[5]</sup>

- Doping: Certain dopants can reduce the wake-up effect.<sup>[6]</sup>

- Pre-conditioning: A "wake-up" protocol with unipolar high-voltage fields can be performed as a pre-conditioning step to stabilize the polarization before device operation.<sup>[11]</sup>

## Q4: After the wake-up phase, my device suffers from fatigue, where the $P_r$ steadily decreases, leading to endurance failure. What is the root cause?

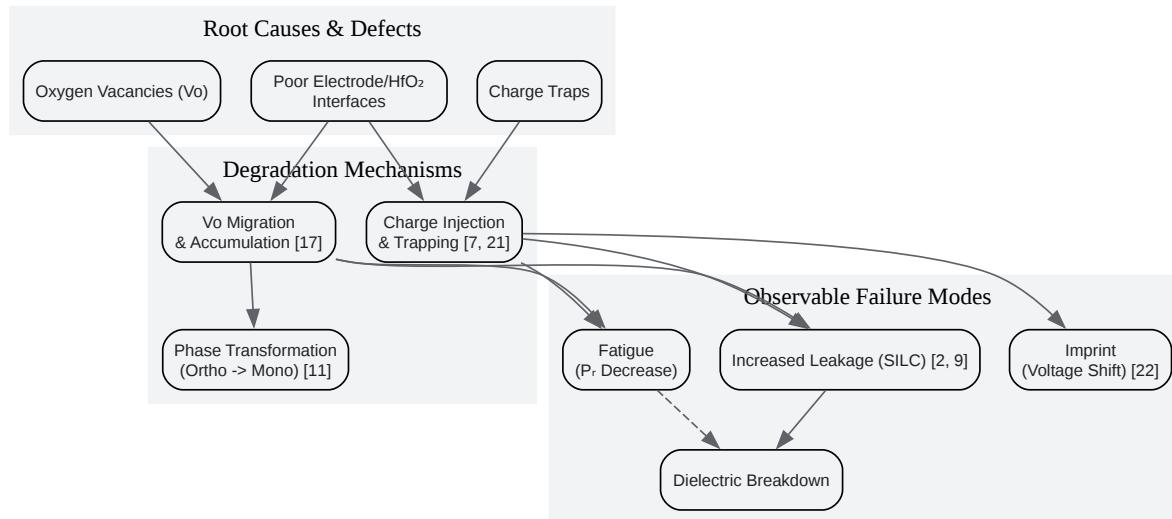

A4: Fatigue is the degradation of switchable polarization with continued cycling and is a primary limiter of device endurance. In  $\text{HfO}_2$ , this is often not due to the ferroelectric material itself "wearing out," but rather to degradation of the entire device stack, particularly the interfaces.[12][13]

Causality & Troubleshooting:

- Charge Trapping & Trap Generation: This is a leading cause of endurance failure.[12] During cycling, high electric fields cause charge injection from the electrodes into the dielectric stack. These charges get trapped, primarily at the  $\text{HfO}_2$ /interfacial layer boundary.[14] This trapped charge creates a bias field that screens the ferroelectric polarization and can eventually prevent switching, thus reducing the memory window.[12]

- Increased Leakage Current: Cycling can generate defects that lead to an increase in stress-induced leakage current (SILC).[15][16] This leakage path can shunt the device, making it impossible to apply the required field for switching and eventually leading to dielectric breakdown.

- Phase Transformation to Monoclinic: Under prolonged electrical stress, there is evidence that the ferroelectric orthorhombic phase can degrade into the non-ferroelectric monoclinic phase, leading to a permanent loss of polarization.[8][17]

Logical Relationship: From Defects to Device Failure

[Click to download full resolution via product page](#)

Caption: Key degradation pathways in  $\text{HfO}_2$  memory devices.

**Q5: My device shows a significant imprint effect, where the hysteresis loop shifts along the voltage axis after being left in one polarization state. How can I minimize this?**

A5: Imprint is a critical reliability issue that can lead to write or retention failure. It is caused by the buildup of an internal bias field ( $E_i$ ) that stabilizes one polarization state over the other, making it harder to switch back.[\[18\]](#)

Causality & Troubleshooting:

- Asymmetric Charge Trapping: The primary cause is the accumulation of trapped charges at or near the ferroelectric/dielectric interfaces. This charge layer creates the internal field.[\[18\]](#)

- Oxygen Vacancy Redistribution: The migration of charged oxygen vacancies under an applied field can also contribute to a stable internal bias.[19]

- Interface Quality: Imprint is highly sensitive to the quality of the interfaces. A thicker or more defective interfacial layer (like  $\text{SiO}_2$ ) can exacerbate charge trapping and, consequently, the imprint effect.[7]

Minimization Strategies:

- Symmetric Interfaces: Fabricate devices with symmetric electrode materials and interfaces to reduce preferential charge injection.

- Interface Layer Optimization: While a thin interfacial layer is often necessary in FeFETs, its thickness and quality must be carefully controlled. Thicker interfaces can improve endurance but may worsen retention and imprint.[7]

- Pulse Scheme Optimization: Using specific voltage pulse schemes for writing and reading can help mitigate the effects of imprint during operation.

## Section 3: Data Tables & Experimental Protocols

**Table 1: Impact of Annealing Temperature on  $\text{HfO}_2$  Device Properties**

| Annealing Temp. | Predominant Phase            | Typical $P_r$ ( $\mu\text{C}/\text{cm}^2$ ) | Wake-Up Effect                             | Endurance          |

|-----------------|------------------------------|---------------------------------------------|--------------------------------------------|--------------------|

| < 500°C         | Amorphous / Monoclinic       | ~0 (Non-ferroelectric)                      | N/A                                        | N/A                |

| 500 - 800°C     | Orthorhombic (Ferroelectric) | 10 - 25                                     | Present, but decreases with higher temp[5] | Optimal            |

| > 850°C         | Monoclinic                   | ~0 (Loss of ferroelectricity)[1]            | N/A                                        | Poor (breaks down) |

Note: Specific temperatures and  $P_r$  values are highly dependent on the dopant, thickness, and electrode materials used.

## Protocol 1: Characterizing Endurance and Fatigue

This protocol outlines the standard methodology for assessing the endurance of a ferroelectric capacitor.

### Equipment:

- Probe station

- Precision LCR meter or Ferroelectric Tester (e.g., Radiant Technologies, Aixacct)

- Pulse Generator

### Methodology:

- Initial Characterization:

- Measure a fresh P-E hysteresis loop on an untested device. Record the initial positive and negative  $P_r$  and  $E_e$  values.

- This serves as the baseline ( $N=1$  cycle).

- Wake-Up/Fatigue Cycling:

- Apply a bipolar square or triangular waveform with an amplitude exceeding the coercive voltage (e.g.,  $1.5 - 2x V_e$ ).

- The frequency is typically set high (e.g., 10 kHz - 1 MHz) to accelerate the test.

- The number of cycles ( $N$ ) is the primary variable.

- Intermittent P-E Measurement:

- Periodically stop the cycling at logarithmic intervals (e.g.,  $N = 10^1, 10^2, 10^3, 10^4$ , etc.).

- After each interval, measure a new P-E hysteresis loop using the same parameters as the initial measurement.

- Data Analysis:

- Plot the remnant polarization ( $2P_r = |P_{r^+}| + |P_{r^-}|$ ) as a function of the number of cycles on a semi-log plot.

- The "wake-up" phase will show an increase in  $2P_r$ .

- The "fatigue" phase will show a decrease in  $2P_r$ .

- Define "endurance failure" as the number of cycles at which  $2P_r$  drops to a certain percentage (e.g., 80%) of its maximum value.

- Leakage Current Monitoring:

- It is highly recommended to also measure the I-V leakage current at each interval. A sudden increase in leakage often precedes or coincides with catastrophic breakdown.[\[16\]](#)

**Need Custom Synthesis?**

BenchChem offers custom synthesis for rare earth carbides and specific isotopic labeling.

Email: [info@benchchem.com](mailto:info@benchchem.com) or [Request Quote Online](#).

## References

- 1. [tud.qucosa.de](http://tud.qucosa.de) [tud.qucosa.de]

- 2. [scispace.com](http://scispace.com) [scispace.com]

- 3. [researchgate.net](http://researchgate.net) [researchgate.net]

- 4. [mdpi.com](http://mdpi.com) [mdpi.com]

- 5. [pubs.aip.org](http://pubs.aip.org) [pubs.aip.org]

- 6. Study of wake-up and fatigue properties in doped and undoped ferroelectric HfO<sub>2</sub> in conjunction with piezo-response force microscopy analysis | IEEE Conference Publication | IEEE Xplore [[ieeexplore.ieee.org](http://ieeexplore.ieee.org)]

- 7. Impact of the interface layer on the cycling behaviour and retention of ferroelectric hafnium oxide [[publica.fraunhofer.de](http://publica.fraunhofer.de)]

- 8. [pubs.acs.org](http://pubs.acs.org) [pubs.acs.org]

- 9. [pubs.acs.org](http://pubs.acs.org) [pubs.acs.org]

- 10. researchgate.net [researchgate.net]

- 11. Effects of Polarization Behavior on Wake-Up and Fatigue of Hafnium-Based Ferroelectric Thin Films - PubMed [pubmed.ncbi.nlm.nih.gov]

- 12. IEEE Xplore Login [ieeexplore.ieee.org]

- 13. researchgate.net [researchgate.net]

- 14. researchgate.net [researchgate.net]

- 15. Impact of specific failure mechanisms on endurance improvement for HfO<sub>2</sub>-based ferroelectric tunnel junction memory | IEEE Conference Publication | IEEE Xplore [ieeexplore.ieee.org]

- 16. Impact of specific failure mechanisms on endurance improvement for HfO<sub>2</sub>-based ferroelectric tunnel junction memory | IEEE Conference Publication | IEEE Xplore [ieeexplore.ieee.org]

- 17. researchgate.net [researchgate.net]

- 18. researchgate.net [researchgate.net]

- 19. Role of oxygen vacancies in ferroelectric or resistive switching hafnium oxide - PMC [pmc.ncbi.nlm.nih.gov]

- To cite this document: BenchChem. [Technical Support Center: Scaling Hafnium Oxide-Based Memory Devices]. BenchChem, [2026]. [Online PDF]. Available at: [<https://www.benchchem.com/product/b10860814#challenges-in-scaling-hafnium-oxide-based-memory-devices>]

---

**Disclaimer & Data Validity:**

The information provided in this document is for Research Use Only (RUO) and is strictly not intended for diagnostic or therapeutic procedures. While BenchChem strives to provide accurate protocols, we make no warranties, express or implied, regarding the fitness of this product for every specific experimental setup.

**Technical Support:** The protocols provided are for reference purposes. Unsure if this reagent suits your experiment? [[Contact our Ph.D. Support Team for a compatibility check](#)]

**Need Industrial/Bulk Grade?** [Request Custom Synthesis Quote](#)

# BenchChem

Our mission is to be the trusted global source of essential and advanced chemicals, empowering scientists and researchers to drive progress in science and industry.

## Contact

Address: 3281 E Guasti Rd

Ontario, CA 91761, United States

Phone: (601) 213-4426

Email: [info@benchchem.com](mailto:info@benchchem.com)