# Technical Support Center: N,N'-Dimethylquinacridone (DMAQ) Transistors

**Author:** BenchChem Technical Support Team. **Date:** December 2025

## Compound of Interest

Compound Name: *N,N'-Dimethylquinacridone*

Cat. No.: *B100281*

[Get Quote](#)

This technical support center provides troubleshooting guidance and frequently asked questions (FAQs) to assist researchers in reducing leakage current in **N,N'-Dimethylquinacridone (DMAQ)** organic thin-film transistors (OTFTs).

## Frequently Asked Questions (FAQs)

**Q1:** What are the primary sources of leakage current in my DMAQ transistor?

Leakage current in OTFTs, including those based on DMAQ, can be broadly categorized into three main paths:

- Gate Leakage Current (IG): This is the current that flows through the gate dielectric layer. It is often caused by a thin or poor-quality dielectric with pinholes or defects, or by high electric fields causing phenomena like Poole-Frenkel emission.<sup>[1]</sup>

- Source-Drain Leakage Current (I<sub>off</sub>): This is the current flowing between the source and drain electrodes when the transistor is in its "off" state. A high I<sub>off</sub> reduces the ON/OFF current ratio, a critical performance metric. This can be caused by charge traps at the semiconductor-dielectric interface, impurities in the semiconductor, or a semiconductor layer that is too thick.<sup>[2]</sup>

- Parasitic Leakage Paths: If the organic semiconductor is not patterned and covers the entire substrate, it can create unintended conduction paths between devices or from the source/drain electrodes to the gate, especially on common gate substrates.<sup>[3][4]</sup>

Q2: My gate leakage current ( $I_G$ ) is significantly high. How can I reduce it?

High gate leakage is almost always related to the quality and properties of the gate dielectric.

Consider the following solutions:

- Improve Dielectric Quality: Thermally grown silicon dioxide ( $\text{SiO}_2$ ) can have pinholes.<sup>[5]</sup> Techniques like Atomic Layer Deposition (ALD) for materials such as aluminum oxide ( $\text{Al}_2\text{O}_3$ ) can produce higher quality, denser films with fewer defects.<sup>[5]</sup>

- Increase Dielectric Thickness: A thicker dielectric layer can reduce the electric field across it, thereby lowering leakage.<sup>[3]</sup> However, this may require higher operating voltages.

- Use a Dielectric Capping Layer: For DMQA transistors, using a thin capping layer of a hydrophobic material like tetratetracontane (TTC) over the primary dielectric (e.g.,  $\text{Al}_2\text{O}_3$ ) can provide an additional barrier to leakage current.<sup>[6]</sup>

- Employ Polymer Blends: For polymeric gate insulators like poly(vinyl phenol) (PVP), using a binary blend of two different molecular weights can reduce the free volume in the film, leading to a more robust, cross-linked layer with lower leakage.<sup>[7]</sup>

Q3: The off-current ( $I_{off}$ ) in my device is high, resulting in a poor ON/OFF ratio. What are the likely causes and solutions?

A high off-current is typically associated with the semiconductor layer and its interface with the dielectric.

- Pattern the Semiconductor: This is one of the most effective methods. If the DMQA layer extends well beyond the channel region between the source and drain, it creates a large area for leakage.<sup>[3][4]</sup> Confining the semiconductor to the channel region eliminates these parasitic paths.<sup>[3]</sup> For lab-scale devices, this can be done by scratching away the excess semiconductor around the active area.<sup>[4]</sup>

- Optimize Semiconductor Thickness: A thicker semiconductor film can lead to higher bulk conductivity and increased off-current.<sup>[2]</sup> Experiment with reducing the thickness of the deposited DMQA layer.

- Improve the Dielectric-Semiconductor Interface: The surface roughness of the dielectric can create charge traps that degrade performance.[\[2\]](#) Furthermore, a high density of trap sites at this interface can result in hysteresis and increased leakage.[\[3\]](#) Surface treatments on the dielectric before DMQA deposition can passivate these traps.

Q4: Can the choice of dielectric capping layer specifically affect leakage in DMQA transistors?

Yes. Research on N,N'-substituted quinacridones has shown that a dielectric capping layer is beneficial. In one study, DMQA transistors were fabricated on an aluminum oxide dielectric.[\[6\]](#) The addition of a 20 nm layer of tetratetracontane (TTC) via physical vapor deposition on top of the oxide provided an additional barrier to leakage, allowing the devices to be scanned to higher voltages before significant leakage occurred.[\[6\]](#)

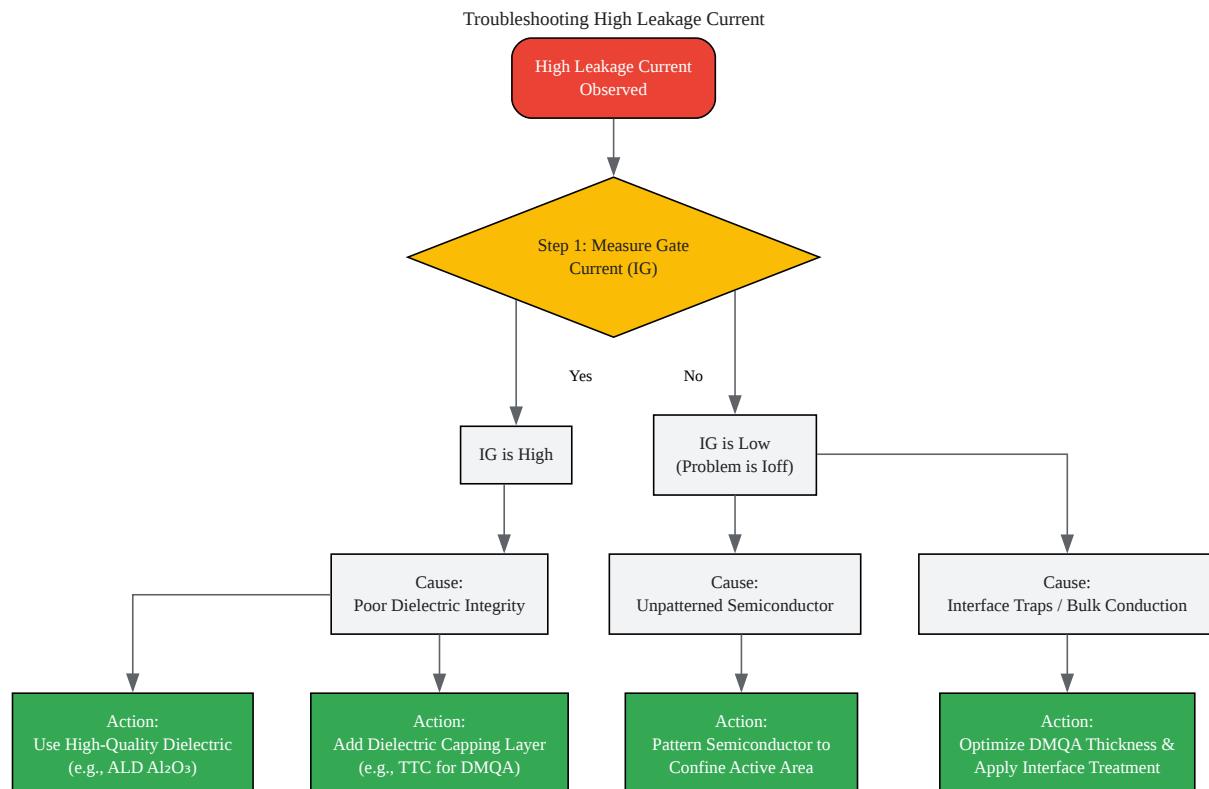

## Troubleshooting Guide

If you are experiencing high leakage current, follow this logical workflow to diagnose and address the issue.

[Click to download full resolution via product page](#)

Caption: A flowchart for diagnosing the root cause of high leakage current.

## Data Presentation

Table 1: Typical Electrical Performance of **N,N'-Dimethylquinacridone (DMAQ)** OFETs

| Parameter                                  | Value                                                         | Device Structure / Dielectric                          |

|--------------------------------------------|---------------------------------------------------------------|--------------------------------------------------------|

| Hole Field-Effect Mobility ( $\mu_h$ )     | $8 \times 10^{-3} \text{ cm}^2 \text{ V}^{-1} \text{ s}^{-1}$ | Top-Contact architecture with AlOx + TTC dielectric[8] |

| Electron Field-Effect Mobility ( $\mu_e$ ) | $3 \times 10^{-4} \text{ cm}^2 \text{ V}^{-1} \text{ s}^{-1}$ | Top-Contact architecture with AlOx + TTC dielectric[8] |

| Dielectric Capacitance                     | $103 \text{ nF cm}^{-2}$                                      | AlOx capped with tetratetracontane (TTC)[8]            |

Table 2: Summary of Strategies to Mitigate Leakage Current

| Strategy                 | Primary Mechanism                                                             | Key Experimental Parameters                                                                                        | Expected Outcome                                                              |

|--------------------------|-------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|

| Dielectric Optimization  | Reduce current paths through the gate insulator.[5]                           | Material choice (Al <sub>2</sub> O <sub>3</sub> , high-k polymers), deposition method (e.g., ALD), film thickness. | Lower gate leakage current (IG).                                              |

| Semiconductor Patterning | Eliminate parasitic conduction paths outside the transistor channel.[3][4]    | Patterning method (shadow mask, photolithography, etching), alignment precision.                                   | Drastic reduction in off-current (I <sub>off</sub> ) and crosstalk.           |

| Interface Engineering    | Passivate charge trapping sites at the semiconductor-dielectric interface.[3] | Surface treatment (e.g., SAMs), choice of dielectric material, surface roughness control.                          | Lower I <sub>off</sub> , reduced hysteresis, and improved subthreshold swing. |

| Dielectric Capping Layer | Add a secondary barrier to prevent current leakage.[6]                        | Capping material (e.g., TTC, beeswax), thickness.                                                                  | Reduced gate leakage, especially at higher operating voltages.[6]             |

## Experimental Protocols

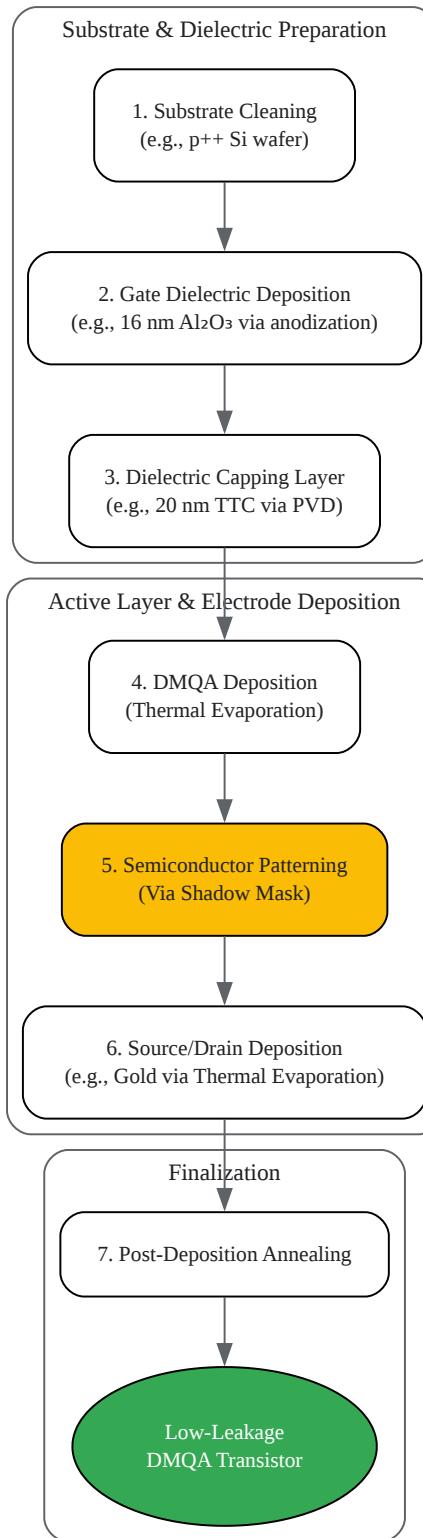

### Protocol 1: Fabrication of a Low-Leakage Bottom-Gate, Top-Contact (BGTC) DMQA Transistor

This protocol outlines key steps with an emphasis on minimizing leakage current.

## Experimental Workflow for Low-Leakage DMQA Transistors

[Click to download full resolution via product page](#)

Caption: Key fabrication steps highlighting critical leakage-reduction stages.

## Methodology Details:

- Substrate Preparation: Begin with a heavily doped silicon wafer (acting as the common gate) with a thermally grown  $\text{SiO}_2$  layer. Clean the substrate sequentially in ultrasonic baths of deionized water, acetone, and isopropanol.

- Gate Dielectric Formation: A high-quality gate dielectric is critical. For DMQA, an aluminum oxide ( $\text{Al}_2\text{O}_3$ ) layer (~16 nm) can be generated via anodization.<sup>[6]</sup> This provides a robust insulating layer.

- Dielectric Capping (Recommended): To further suppress gate leakage, deposit a thin (e.g., 20 nm) layer of tetratetracontane (TTC) via physical vapor deposition (PVD).<sup>[6]</sup> This adds a hydrophobic, insulating layer that improves the interface for subsequent organic deposition.

- DMQA Deposition: Thermally evaporate **N,N'-Dimethylquinacridone** onto the substrate in a high-vacuum chamber. Maintain a low deposition rate (e.g., 0.1-0.2 Å/s) to ensure a well-ordered film. The final thickness should be optimized (typically 30-50 nm).

- Semiconductor Patterning (CRITICAL STEP): To prevent parasitic leakage paths, the DMQA layer must be patterned.<sup>[3][4]</sup> This is most easily achieved by performing the deposition through a shadow mask, confining the active material only to the desired channel areas of the devices.

- Source/Drain Electrode Deposition: Deposit the top-contact source and drain electrodes (e.g., 50 nm of Gold) via thermal evaporation through a shadow mask. The channel length (L) and width (W) are defined by this mask.

- Annealing and Characterization: Anneal the completed devices in a nitrogen environment to improve film morphology and contact quality. Characterize the devices using a semiconductor parameter analyzer, specifically measuring the transfer and output characteristics to determine Ion/Ioff ratio, mobility, and threshold voltage. Pay close attention to the gate current (IG) during sweeps to verify low leakage.

**Need Custom Synthesis?**

BenchChem offers custom synthesis for rare earth carbides and specific isotopic labeling.

Email: [info@benchchem.com](mailto:info@benchchem.com) or [Request Quote Online](#).

## References

- 1. researchgate.net [researchgate.net]

- 2. researchgate.net [researchgate.net]

- 3. mdpi-res.com [mdpi-res.com]

- 4. researchgate.net [researchgate.net]

- 5. researchgate.net [researchgate.net]

- 6. N , N '-Substituted quinacridones for organic electronic device applications - Materials Advances (RSC Publishing) DOI:10.1039/D2MA01010K [pubs.rsc.org]

- 7. researchgate.net [researchgate.net]

- 8. researchgate.net [researchgate.net]

- To cite this document: BenchChem. [Technical Support Center: N,N'-Dimethylquinacridone (DMQA) Transistors]. BenchChem, [2025]. [Online PDF]. Available at: [<https://www.benchchem.com/product/b100281#reducing-leakage-current-in-n-n-dimethylquinacridone-transistors>]

---

### Disclaimer & Data Validity:

The information provided in this document is for Research Use Only (RUO) and is strictly not intended for diagnostic or therapeutic procedures. While BenchChem strives to provide accurate protocols, we make no warranties, express or implied, regarding the fitness of this product for every specific experimental setup.

**Technical Support:** The protocols provided are for reference purposes. Unsure if this reagent suits your experiment? [[Contact our Ph.D. Support Team for a compatibility check](#)]

**Need Industrial/Bulk Grade?** [Request Custom Synthesis Quote](#)

# BenchChem

Our mission is to be the trusted global source of essential and advanced chemicals, empowering scientists and researchers to drive progress in science and industry.

## Contact

Address: 3281 E Guasti Rd

Ontario, CA 91761, United States

Phone: (601) 213-4426

Email: [info@benchchem.com](mailto:info@benchchem.com)